| PGA |

1~2048 |

| INTN/GPIO |

16 |

| Watch Dog |

YES |

| MCU |

Arm M0+ |

| DAC (bit) |

12 |

| CTRL IF |

IIC/UART |

| Low Power Mode |

YES |

| Channel |

10 |

| Temperature |

-40℃~105℃ |

| Package (mm) |

QFN 5X5-40L |

| ADC (bit) |

14 |

24MHz ARM®CortexTM-M0+

4KB LDROM, 60KB Flash, 16KB SRAM

Selectable Gains of 1, …, 2048

100 K SPS 14-bit SAR ADC

12-bit offset calibration DAC

CRC32 and High-speed divider

2 x 24-bit timer, 2 watch-dog

Support 1MHz I2C, UART

I2C 7-bit slave address:0x5C

Max 10 analog input channel, 16 GPIO pins

Power-on reset, Low voltage detection

Low voltage reset and temperature detection

Support In-System Programming (ISP) & In-Circuit Programming (ICP)

Low power mode

AEC-Q100 Temperature Range:

Grade2 (-40℃~105℃)

WBQFN 5.0mmX5.0mmX0.75mm-40L package

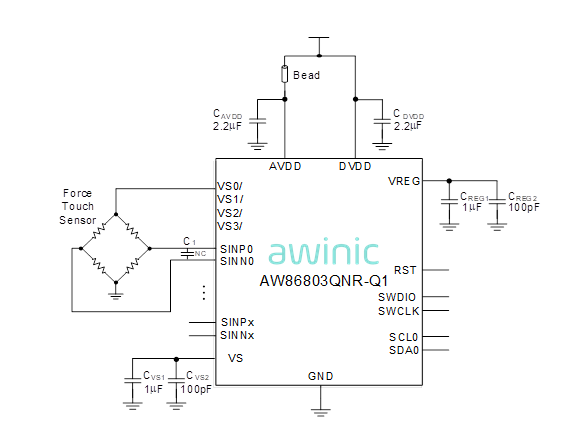

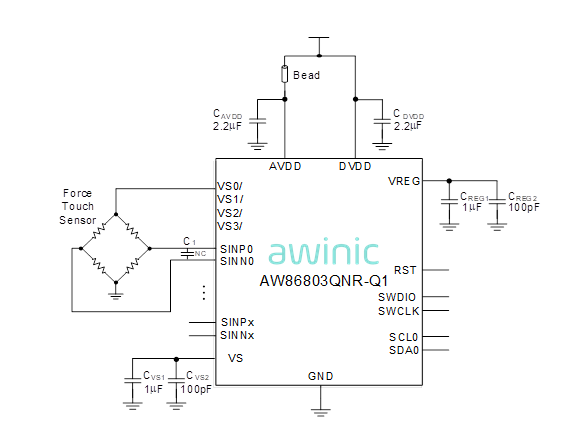

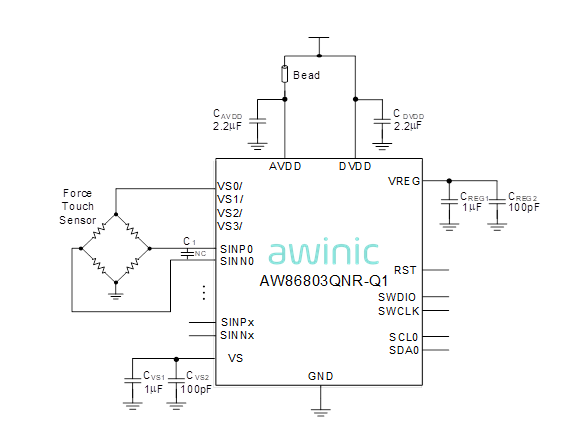

AW86803QNR-Q1 is a SoC for force sensing front-end data acquisition, processing and control, which is integrated ARM®CortexTM-M0+ core. It has embedded 60k byte program flash (APROM), 4k byte boot program space LDROM, 16k byte SRAM. It integrated timer, watch dog, 1 AFE module, 1 I2C module, 1 UART module and 1 GPIO module.

AW86803QNR-Q1 support ISP (In-System Programming) and ICP (In-Circuit Programming). System startup interval is configurable, It can be configured to boot from ROM, LDROM in SRAM.